Abstract

Verilog語法介紹,在使用前必須先宣告暫存器的位元數大小與數量,在此將介紹幾個常用的定義方式。

jk3527101 發表在 痞客邦 留言(0) 人氣(23,379)

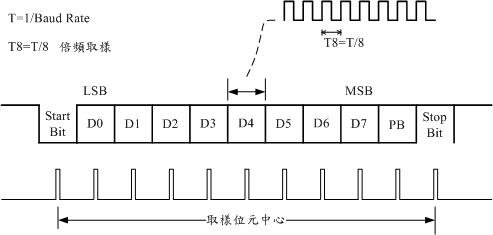

UART Protocol Introduction引用先前的文章

UART Protocol Introduction引用先前的文章 鮑率

(Baud Rate)jk3527101 發表在 痞客邦 留言(2) 人氣(12,774)

UART Protocol IntroductionAbstract :現今許多微處理器(Microcontroller)內部都有函數提供使用者使用,僅需要對特定的暫存器進行設定即可使用,但未來若需要降低成本又或者是其他因素的考量都是有機會需要去撰寫的。若需要自行撰寫串列傳輸(UART)的輸出(TX)與輸入(RX),通訊協定的基本認知是不可以沒有的。

UART Protocol IntroductionAbstract :現今許多微處理器(Microcontroller)內部都有函數提供使用者使用,僅需要對特定的暫存器進行設定即可使用,但未來若需要降低成本又或者是其他因素的考量都是有機會需要去撰寫的。若需要自行撰寫串列傳輸(UART)的輸出(TX)與輸入(RX),通訊協定的基本認知是不可以沒有的。 jk3527101 發表在 痞客邦 留言(0) 人氣(12,910)

定點數運算(Fixed Point)Abstract :定點數(Fixed-Point)運算是指利用整數運算模擬浮點數(Floating-point)運算,雖然會降低精確度,卻可以提升微處理器的運算速度。在現今一般的微處理器內並沒有配置浮點數的運算器,浮點數運算需要花費較多的時間,對於控制理論而言,程式執行的時間必須十分嚴謹。可以利用較短的時間完成較多的事情是定點數運算的優點之一。

定點數運算(Fixed Point)Abstract :定點數(Fixed-Point)運算是指利用整數運算模擬浮點數(Floating-point)運算,雖然會降低精確度,卻可以提升微處理器的運算速度。在現今一般的微處理器內並沒有配置浮點數的運算器,浮點數運算需要花費較多的時間,對於控制理論而言,程式執行的時間必須十分嚴謹。可以利用較短的時間完成較多的事情是定點數運算的優點之一。jk3527101 發表在 痞客邦 留言(0) 人氣(19,944)

鮑率(Baud Rate)

Abstract :

學習串列傳輸(UART)時總想問說,什麼是鮑率(Baud Rate)?

jk3527101 發表在 痞客邦 留言(0) 人氣(33,970)

Abstract

Verilog入門玩家的常見問題 : 何時該用wire?何時又該改用reg?

jk3527101 發表在 痞客邦 留言(2) 人氣(3,142)

簡介RS-232 & RS-485

_RS232_

1) 全雙工傳輸

jk3527101 發表在 痞客邦 留言(1) 人氣(8,370)

階層式設計

將模組的埠與外部訊號連接的方法有兩種,分別是:依照定義模組時埠列的「順序」(in order)來連接,以及依「指定名稱」(by name)的方法來連接。這兩種方法必須分開使用,不可以同時在相同模組中使用。

jk3527101 發表在 痞客邦 留言(1) 人氣(6,745)

If-else條件敘述

Exp:

If(<條件式>)

jk3527101 發表在 痞客邦 留言(0) 人氣(9,638)

APEC 2012

(The Applied Power Electronics Conference and Exposition)

我又來了! 又來了? 是的,這是我第三次踏上美國的土地,為了實現夢想又再度的踏上了這段漫長的旅程,長達20個小時的飛行時數,真的不是普通的累!! 再加上時差的因素,早也想睡、晚也想睡,怎樣都睡不飽的那種疲憊,難以言語。

jk3527101 發表在 痞客邦 留言(1) 人氣(85)